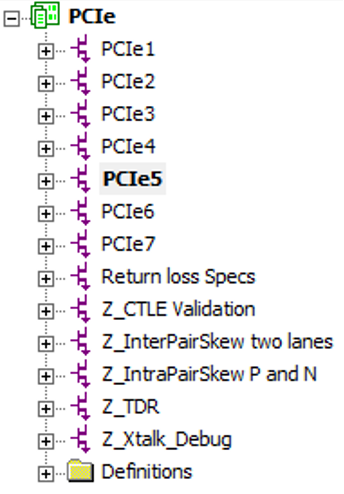

Fig 2: PCIe Template covers PCIe 1-7 standards

This template is available for purchase by Ansys users to validate designs and simulations against any PCIe standard. The template contains a built-in ready-to-use model based on the standards covering:

• Data rate

• Rising time

• Voltage amplitude

• FFE (Feed-forward Equalization)

• DFE (Decision forward Equalization)

• CTLE (Continuous Time Linear Equalization) with variable gain

• NRZ/PAM4

• eye width spec

• eye height spec

• return loss spec

• PN skew

• Inter-Pair skew

• Non-equalized eye calculations

• Stressed eye analysis

• Crosstalk debugging capability

The only input required is the s-parameters of a full/partial link.

This template takes care of all associated pre and post-processing.

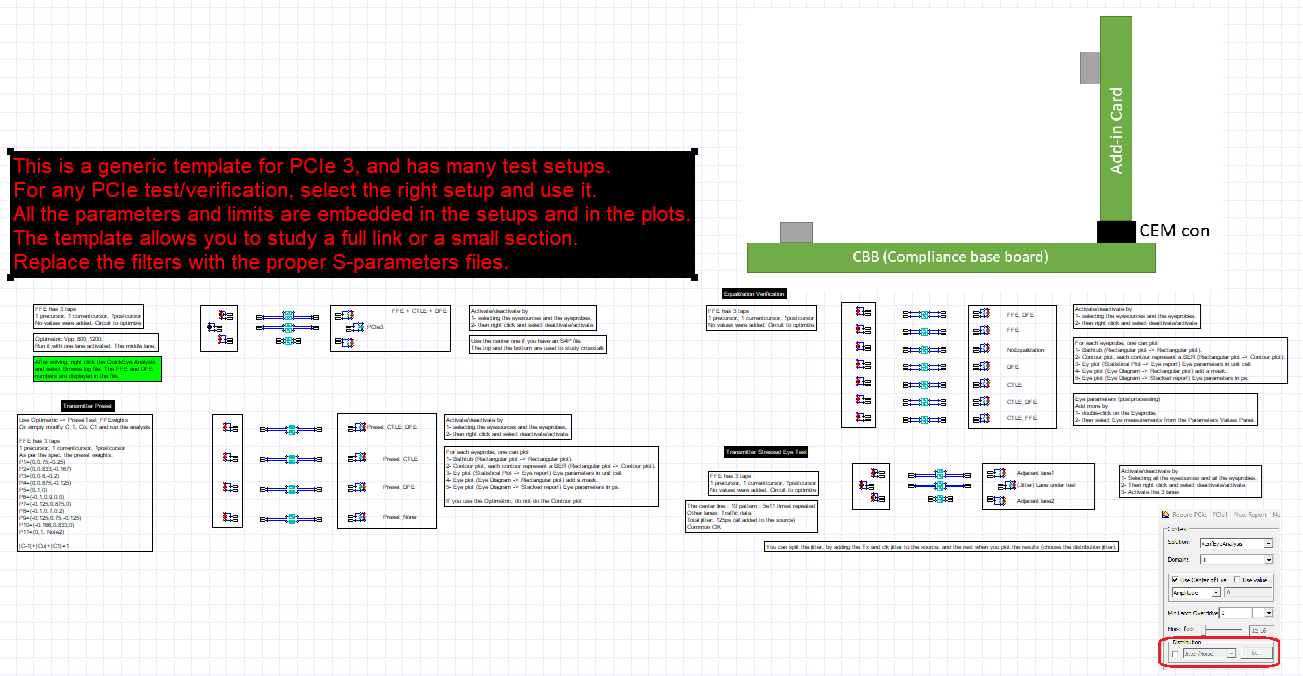

Fig 3: All pre and post-processing for PCIe analysis is preset

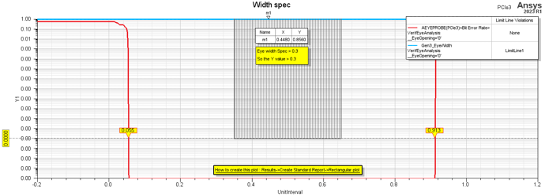

The PCIe specification requires that the width of the eye should be greater than 0.3UI at 1e-12BER.

The template plots the bathtub to determine the width of the eye at 1e-12BER.

Fig 4: Bathtub with eye-width spec predefined.

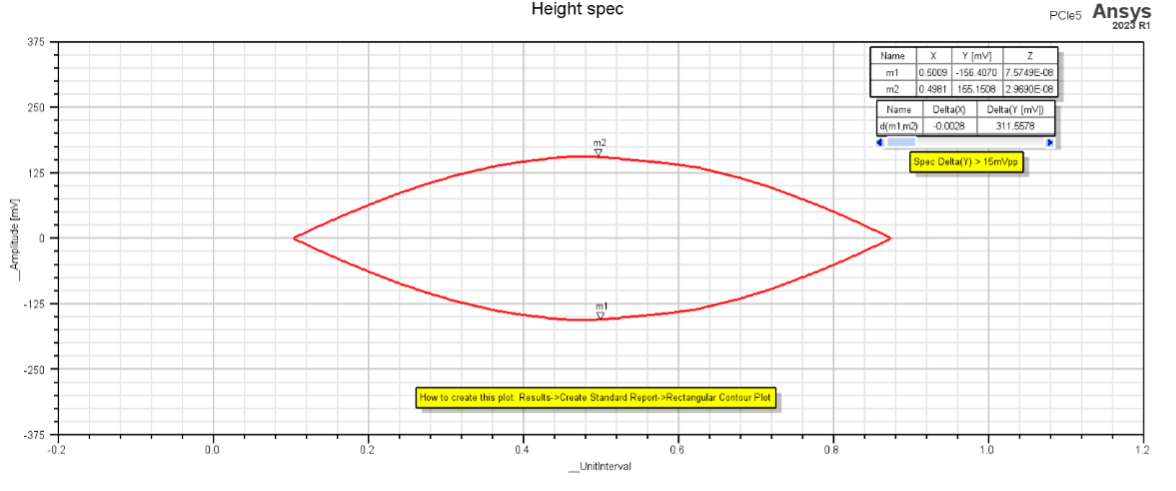

The PCIe specification requires that the height of the eye should be greater than 15mVpp at 1e-12BER.

The template uses the contour plot to determine the height of the eye at 1e-12BER.

Fig 5: Eye diagram with eye-height spec predefined.

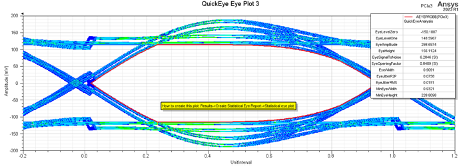

The PCIe does not specify all the parameters of an eye, but the designer has to calculate all the parameters of the eye and look for any deficiency signature on the eye.

Each signature has a meaning; Bad transition, change in impedance, crosstalk, Jitter, and other irregular phenomena.

Fig 6: Eye diagram with eye parameters (Level zero, Level 1, Amplitude, and Jitter).

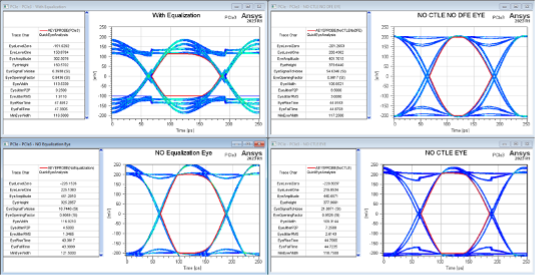

PCIe uses equalization, and there are rules. A limited number of taps are allowed on the RX and the Tx sides.

The equalization parameters are all programmed inside the template for each standard. Sometimes users do not want to use equalization because the lines have enough bandwidth.

They want to know the effect of removing all or part of the equalization. Such a study can be done with the provided template.

Fig 7: Eye diagram with eye parameters for the case of no-equalization/partial equalization/full equalization

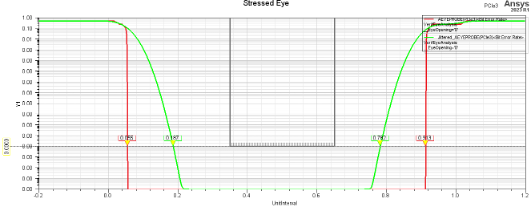

They stressed eye analysis. HFSS allows the user to add Jitter and noise to the RX received eye. One can add random/sinusoidal/deterministic/DCD jitter or noise. Users can then study the eye width of the signal under stress.

Fig 8: Stressed eye analysis and ey-width verification against the PCE spec

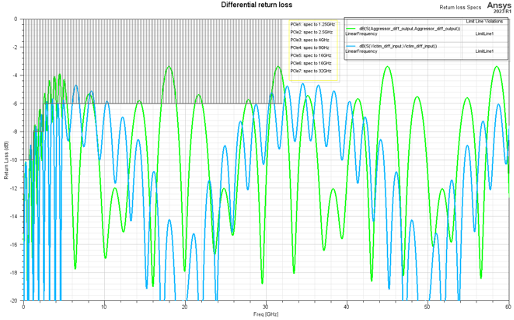

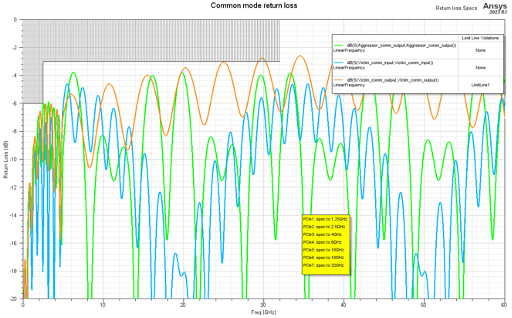

PCIE also specifies the return loss, differential return loss, and common mode return loss. Each standard has its specifications extended to a frequency point. The specifications of all the standards are shown in the plots below.

Fig 8: Differential mode return loss specifications

Fig 9: Common mode return loss specifications

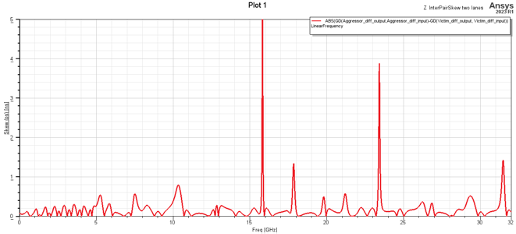

PCIe has no spec on the skew between lines, but users would like to keep them equal. The template calculates the skew based on the group delay of the differential mode.

Fig 10: Interpair skew between two PCIe lines

PCIe has no spec on the PN skew between lines, but users would like to keep it as low as possible on all PCIe lines. The template calculates the PN skew based on the common and differential insertion.

Fig 11: P/Nr skew between two PCIe lines

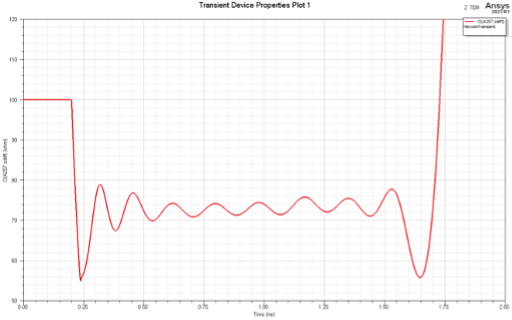

For designers, it is important to locate any deficiencies in the design of the PCIe lines. Some imperfections are tolerable, but others are not. TDR analysis will expose any issues in the design.

Fig 12: TDR results of the line to identify impedance/transition irregularities.